# LUMISSIL MICROSYSTEMS

#### **SMART LED CONTROLLER**

January 2024

#### **GENERAL DESCRIPTION**

IS32FL3202 is a three channel LED controller. Each LED channel supports 6-bit DC (Dot Correction) current adjustment for color setting and 12-bit PWM for smooth LED dimming control.

The maximum output current of each LED channel (for R, G, B) is 63mA. All registers in the IS32FL3202 can be accessed via a Lumissil proprietary bus (Lumibus). IS32FL3202 supports LAA (Location Address Assignment) for random LED driver access without address pins.

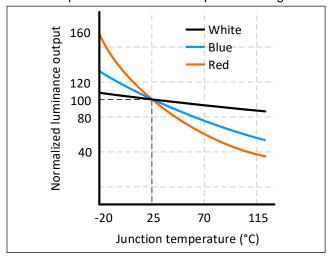

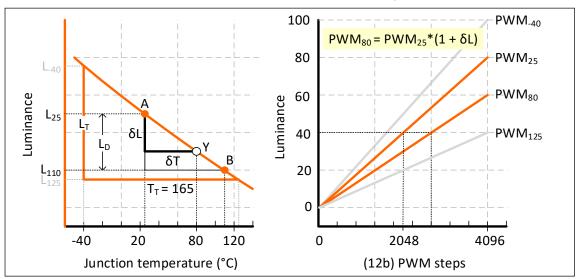

IS32FL3202 can measure the LED chip temperature, which is applied to the built-in temperature compensation algorithm to provide constant luminance over wide operating temperature range. After temperature compensation, final PWM data is kept to 16-bit for more precise color presentation.

To minimize the EMI, IS32FL3202 supports spread spectrum in the PWM clock generator.

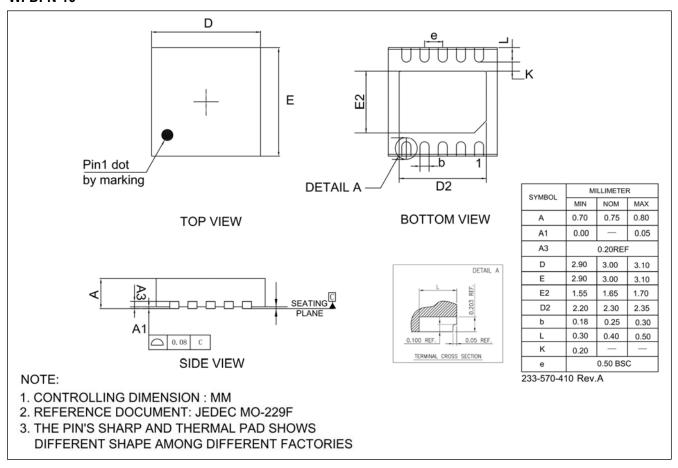

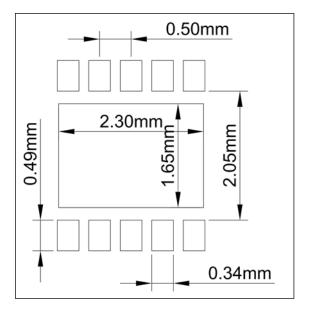

IS32FL3202 is available in WFDFN-10 (3mm×3mm), operates from 3.5V to 6.5V over the temperature range of -40°C to +125°C.

#### **APPLICATIONS**

- Automotive Ambient lighting

- Automotive Roof lighting

- Automotive Functional lighting

#### **FEATURES**

- 3.5V to 6.5V supply

- Built-in LDO to power on chip logic circuit operation

- Three 63mA R, G, B LED (1 RGB dot) drivers

- Lumissil's proprietary Lumibus supports 5V LUMI PHY and UART protocol layer for communication up to 2MHz for 128 devices or up to 1MHz for 254 devices

- LAA (Location Address Assignment) for random IS32FL3202 access without address pins, up to 254 devices can be addressed in a chain

- Broadcast mode allows all of slave devices to be addressed simultaneously

- Support 6-bit DC for each channel

- Support 12-bit PWM input data for each channel

- After temperature compensation, final PWM data is 16-bit for each channel

- Support on die OTP for binning data storage with built-in algorithm to assist fast binning production

- Support spread spectrum to reduce EMI

- Support noise reduction algorithm to minimize power ripple

- Two field PWM mode allows easier dimming and cross fading ambient light effect operation

- Provide constant luminance over wide temperature range by temperature compensation algorithm

- LED open/short detection

- Support thermal shutdown protection

- VCC under-voltage detection

- AEC-Q100 Qualified with Temperature Grade 1: -40°C to 125°C

- Operating temperature: -40°C to 125°C

- WFDFN-10 (3mm×3mm) package

- RoHS & Halogen-Free Compliance

- TSCA Compliance

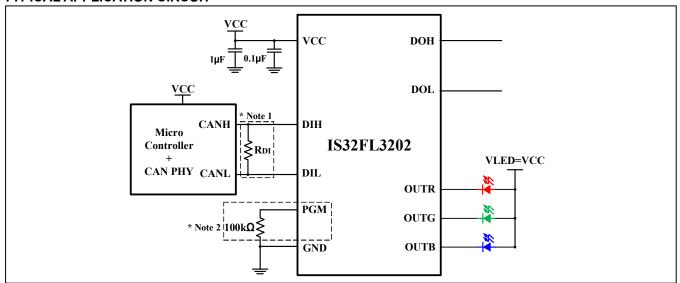

#### TYPICAL APPLICATION CIRCUIT

Figure 1 Typical Application Circuit

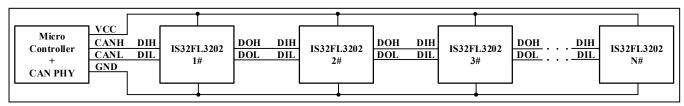

Figure 2 Typical Application Circuit (Cascade)

Note 1: It is recommended to use  $120\Omega$  for this resistor.

**Note 2:** During the whole on die OTP programming procedure, an external programming voltage of 4.6V~4.8V must be applied to the PGM pin and needs decoupling capacitor, and the PGM pin is recommended pull down to GND through a resistor after on die OTP programming done.

### **PIN CONFIGURATION**

| Package  | Pin Configuration (Top View)                                                                                |  |  |

|----------|-------------------------------------------------------------------------------------------------------------|--|--|

| WFDFN-10 | DIH 1   0   10   PGM  DIL 2         9   DOH  OUTG 3       8   DOL  OUTR 4         7   VCC  OUTB 5   6   GND |  |  |

### **PIN DESCRIPTION**

| No. | Pin         | Description                             |  |

|-----|-------------|-----------------------------------------|--|

| 1   | DIH         | Lumibus differential input High level.  |  |

| 2   | DIL         | Lumibus differential input Low level.   |  |

| 3   | OUTG        | Green LED driver pin.                   |  |

| 4   | OUTR        | Red LED driver pin.                     |  |

| 5   | OUTB        | Blue LED driver pin.                    |  |

| 6   | GND         | Ground.                                 |  |

| 7   | VCC         | Driver power supply.                    |  |

| 8   | DOL         | Lumibus differential output Low level.  |  |

| 9   | DOH         | Lumibus differential output High level. |  |

| 10  | PGM         | On die OTP program power supply.        |  |

|     | Thermal Pad | Connect to GND.                         |  |

**ORDERING INFORMATION**

Automotive Range: -40°C to +125°C

| Order Part No.      | Package             | QTY/Reel |

|---------------------|---------------------|----------|

| IS32FL3202-DWLA3-TR | WFDFN-10, Lead-free | 2500     |

Copyright © 2023 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage VCC                                                                                                 | -0.3V ~+8V                   |

|--------------------------------------------------------------------------------------------------------------------|------------------------------|

| Voltage at any I/O pin DIH, DIL, DOH, DOL                                                                          | -0.3V ~V <sub>CC</sub> +0.3V |

| Maximum junction temperature, T <sub>JMAX</sub>                                                                    | +150°C                       |

| Storage temperature range, T <sub>STG</sub>                                                                        | -65°C ~ +150°C               |

| Operating temperature range, T <sub>A</sub> =T <sub>J</sub>                                                        | -40°C ~ +125°C               |

| Package thermal resistance, junction to ambient (4-layer standard test PCB based on JESD 51-2A), $\theta_{JA}$     | 53.8°C/W                     |

| Package thermal resistance, junction to thermal PAD (4-layer standard test PCB based on JESD 51-2A), $\theta_{JP}$ | 5.93°C/W                     |

| ESD (HBM)                                                                                                          | 3kV                          |

| ESD (CDM)                                                                                                          | 750V                         |

**Note 3:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

- "♦" This symbol in the table means these limits are guaranteed at room temp T<sub>J</sub>= 25°C.

- "◊" This symbol in the table means these limits are guaranteed at full temp range T<sub>J</sub>= -40°C~125°C.

The following specifications apply for V<sub>CC</sub>= 5V, T<sub>J</sub>= 25°C, unless otherwise noted (Note 4).

| Symbol                | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Conditions                                                             |            | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------|------|------|------|------|

| Vcc                   | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                        |            | 3.5  |      | 6.5  | V    |

| Icc                   | Quiescent power supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | All LEDs off, register set PSM=0                                       |            |      | 7    | 9    | mA   |

| I <sub>PSM</sub>      | Power saving mode current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | All LEDs off, register set PSM=1, enter power saving mode              |            |      | 0.75 | 1    | mA   |

| Louzano               | Maximum constant current of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>OUT</sub> = 0.6V, DC=0x3F,                                      | •          | 61   | 63   | 65   | mA   |

| I <sub>OUT(MAX)</sub> | OUTx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PWM=0xFFF                                                              | $\Diamond$ | 59   | 63   | 67   | mA   |

| $\Delta I_{MAT}$      | Output current error between outputs (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>OUT</sub> = 0.6V, DC=0x3F,<br>PWM=0xFFF, I <sub>OUT</sub> =63mA |            | -3   |      | 3    | %    |

| ۸۱                    | Output current error between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | n V <sub>OUT</sub> = 0.6V, DC=0x3F, ◆                                  |            | -4   |      | 4    | %    |

| ΔIACC                 | devices (Note 6)  Description of the service of the |                                                                        | $\Diamond$ | -6.5 |      | 6.5  | %    |

| $V_{HR}$              | Current sink headroom voltage OUTx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DC=0x3F, PWM=0xFFF, I <sub>OUT</sub> =63mA                             |            |      | 350  | 450  | mV   |

| fout                  | PWM frequency of output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Frequency setting= 244Hz                                               |            | 230  | 244  | 258  | Hz   |

| T <sub>SD</sub>       | Thermal shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (Note 7)                                                               |            |      | 165  |      | °C   |

| T <sub>SD_HYS</sub>   | Thermal shutdown hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (Note 7)                                                               |            |      | 25   |      | °C   |

| V <sub>oc</sub>       | OUTx open threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DC= 0x1E, I <sub>OUT</sub> = 30mA, PWM>1%, measured at OUTx            |            | 220  | 310  |      | mV   |

| Vsc                   | OUTx short threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PWM>1%, measured at (Vcc-Voutx)                                        |            | 400  | 600  |      | mV   |

| I <sub>LEAK</sub>     | R/G/B channel leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>OUTX</sub> = 5V, V <sub>CC</sub> = 5V                           |            |      |      | 0.25 | μA   |

#### **LUMIBUS INTERFACE CHARACTERISTICS (NOTE 7)**

The following specifications apply for T<sub>J</sub>= 25°C, unless otherwise noted (Note 4).

| Symbol               | Parameter                                     | Conditions                                                                                                                                                                                                           | Min.        | Тур.                    | Max.                    | Unit |

|----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------|-------------------------|------|

| Vo nou               | Dominant output voltage                       | V <sub>CC</sub> = 3.5V to 6.5V, wake up modes,<br>R <sub>L</sub> ≥1000Ω, measured at DOH pin                                                                                                                         | Vcc<br>-0.3 | Vcc<br>-0.1             | Vcc                     | V    |

| V <sub>O_DOM</sub>   | Dominant output voltage                       | V <sub>CC</sub> = 3.5V to 6.5V, wake up modes,<br>R <sub>L</sub> ≥1000Ω, measured at DOL pin                                                                                                                         | 0           | 0.1                     | 0.3                     | V    |

| V <sub>DOMSYM</sub>  | Dominant voltage symmetry                     | V <sub>CC</sub> = 3.5V to 6.5V, wake up modes,<br>R <sub>L</sub> ≥1000Ω, V <sub>DOMSYM</sub> = V <sub>CC</sub> -V <sub>DOH</sub> -V <sub>DOL</sub>                                                                   | -200        |                         | +200                    | mV   |

| $V_{TXSYM}$          | Transmitter voltage symmetry                  | $V_{CC}$ = 3.5V to 6.5V, wake up modes, $R_L \ge 1000\Omega$ , $V_{TXSYM} = V_{DOH} + V_{DOL}$                                                                                                                       | Vcc<br>-0.3 |                         | V <sub>CC</sub><br>+0.3 | ٧    |

| V <sub>O_RES</sub>   | Recessive output voltage                      | V <sub>CC</sub> = 3.5V to 6.5V, wake up modes, R <sub>L</sub><br>≥1000Ω, measured at DOH and DOL pin                                                                                                                 |             | 0.5×<br>V <sub>CC</sub> |                         | ٧    |

|                      | Differential output voltage                   | Dominant: $V_{CC}$ = 3.5V to 6.5V, wake up modes, $R_L \ge 1000\Omega$ , $V_{O\_DIF}$ = $V_{DOH}$ - $V_{DOL}$                                                                                                        | 1.5         |                         | Vcc                     | V    |

| $V_{O\_DIF}$         | Differential output voltage                   | Recessive: $V_{CC}$ = 3.5V to 6.5V, wake up modes, $R_L \ge 1000\Omega$ , $V_{O\_DIF} = V_{DOH} - V_{DOL}$                                                                                                           | -50         |                         | +50                     | mV   |

| V <sub>REC_RX</sub>  | Receiver input differential recessive voltage | Recessive: V <sub>CC</sub> = 3.5V to 6.5V, wake up modes, R <sub>L</sub> ≥1000Ω, V <sub>REC_RX</sub> =D <sub>IH</sub> -D <sub>IL</sub> , 0V≤V <sub>DIL</sub> ≤V <sub>CC</sub> , 0V≤V <sub>DIH</sub> ≤V <sub>CC</sub> |             |                         | 0.5                     | ٧    |

| V <sub>DOM_RX</sub>  | Receiver input differential dominant voltage  | Dominant: V <sub>CC</sub> = 3.5V to 6.5V, wake up modes, R <sub>L</sub> ≥1000Ω, V <sub>DOM_RX</sub> = D <sub>IH</sub> -D <sub>IL</sub> , 0V≤V <sub>DIL</sub> ≤V <sub>CC</sub> , 0V≤V <sub>DIH</sub> ≤V <sub>CC</sub> | 0.9         |                         |                         | ٧    |

| V <sub>HYS_DIF</sub> | Differential receiver hysteresis voltage      | $V_{CC}$ = 3.5V to 6.5V, wake up modes, $R_L \ge 1000\Omega$ , $0V \le V_{DIL} \le V_{CC}$ , $0V \le V_{DIH} \le V_{CC}$ (Note 7)                                                                                    |             | 100                     |                         | mV   |

|                      | Dominant short-circuit                        | V <sub>CC</sub> = 3.5V to 6.5V, wake up modes, DOH short to ground, measured DOH pin output current                                                                                                                  |             | -20                     | -15                     | mA   |

| Іо_ром               | output current                                | V <sub>CC</sub> = 3.5V to 6.5V, wake up modes, DOL short to VCC, measured DOL pin output current                                                                                                                     | 15          | 20                      |                         | mA   |

| lo_res               | Recessive short-circuit output current        | V <sub>CC</sub> = 3.5V to 6.5V, DOH short to ground, measured DOH pin output current                                                                                                                                 |             | -1                      |                         | mA   |

|                      |                                               | V <sub>CC</sub> = 3.5V to 6.5V, DOL short to VCC, measured DOL pin output current                                                                                                                                    |             | 1                       |                         | mA   |

| Ri_DIF               | Differential input resistance                 | measured at DIH and DIL pin                                                                                                                                                                                          |             | 1.7                     |                         | kΩ   |

| Ro_DIF               | Differential output resistance                | measured at DOH and DOL pin                                                                                                                                                                                          |             | 1.7                     |                         | kΩ   |

**Note 4:** Limits are 100% production tested at 25°C. Limits over the operating temperature range verified through either bench and/or tester testing and correlation using Statistical methods.

Note 5: lour mismatch (channel to channel)

$$\triangle$$

I<sub>MAT</sub> is calculated:  $\Delta I_{MAT} = \pm \left(\frac{I_{OUT(MAX)} - I_{OUT(MIN)}}{\left(\frac{I_{OUT1} + I_{OUT2} + I_{OUT3}}{3} \times 2\right)}\right) \times 100\%$

Note 6:  $I_{\text{OUT}}$  accuracy (device to device)  $\triangle I_{\text{ACC}}$  is calculated:

$$\Delta I_{ACC} = \left(\frac{I_{OUT(MIN)} - I_{OUT(IDEAL)}}{I_{OUT(IDEAL)}}\right) \times 100\% \sim \left(\frac{I_{OUT(MAX)} - I_{OUT(IDEAL)}}{I_{OUT(IDEAL)}}\right) \times 100\%$$

Where  $I_{OUT(IDEAL)}$ = 63mA

Note 7: Guaranteed by design.

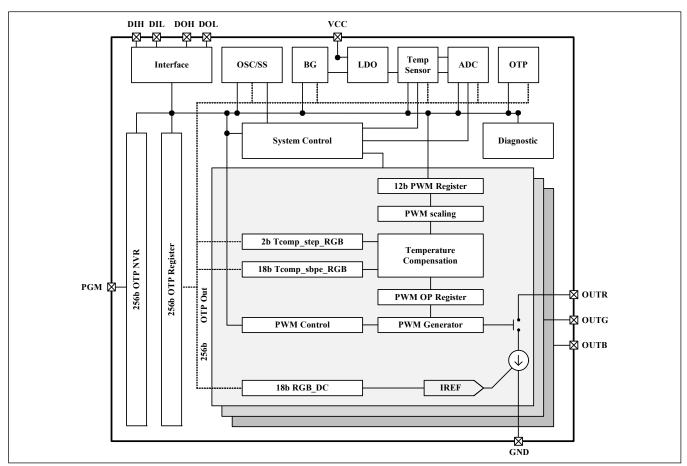

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 3 IS32FL3202 Block Diagram

IS32FL3202 can control R, G, and B LED individually, as shown in the above block diagram. Each LED channel can support up to 63mA current. For the best thermal performance, in addition to a good package thermal resistance and a good multiple layer PCB, an external buck controller is recommended to lower VCC to minimum LED headroom's operating voltage.

Many parameters can be adjusted via a Lumissil proprietary bus, Lumibus, for communication. Lumibus has two major components: LUMI PHY and UART protocol layers. The PHY protocol is based on the simplified, 5V CAN PHY protocol, and is only used to convert CAN PHY like transmission signaling to the ordinary UART signaling for internal processing. More CAN PHY specific features are not supported, such as sleep and wake up signaling.

Because of its differential nature, IS32FL3202's Lumibus offers a very robust and proven communication means, reducing EMI/EMC emission, and less susceptible to external RF interference.

UART protocol is used on the data link layer. In order to send proper controlling parameters to the specific registers of a specific device in the system, each device needs a unique address (Network Address, NAD) and each register needs a unique register address. A Location Address Assignment (LAA) method is used for automatic address assignment. This method allows all identical IS32FL3202 devices in the system to be assigned one unique NAD, which is stored in the on-die OTP permanently. OTP itself is protected by an ECC code for reliable NAD storage.

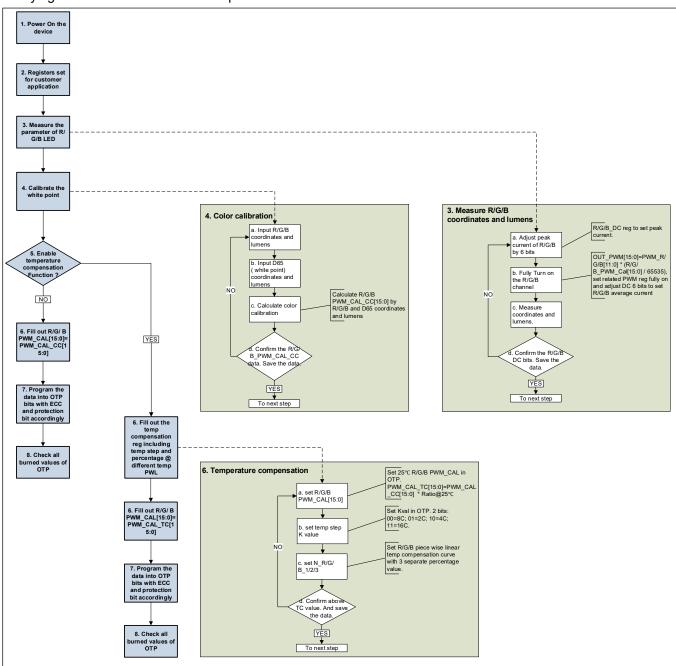

The on-die OTP stores many trimming and calibration parameters, such as binning and temperature compensation information. Lumissil can provide production GUI tools for ease of trimming and calibration production flow.

Additional measures are taken to further reduce EMI emission, such as audible and power ripple reduction method, as well as spread spectrum for PWM modulation, which is very important for commercial and auto applications.

#### **DETAILED DESCRIPTION**

#### **LUMIBUS INTERFACE**

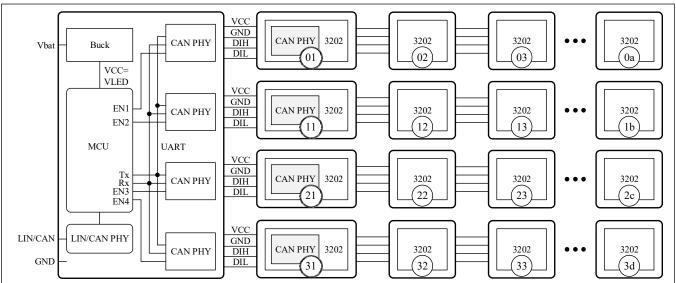

#### **Lumibus System Architecture**

IS32FL3202 uses Lumissil's proprietary Lumibus for communication. Lumibus adopts the matured and proven UART protocol layer and 5V CAN PHY protocol layer. The system host communicates (write and read) with slaves via Lumibus utilizing two signal wires: DIH and DIL as shown in Figure 4. Each chain is connected to the MCU via a commercial CAN PHY.

Figure 4 Lumibus System Topology (One Module In A Zone)

Prior to the system operation, Location Address Assignment (LAA) method is used to automatically assign address for each Lumibus slave device in each chain. LAA address can be stored either in the on-die OTP for permanent storage, so that LAA algorithm only needs to be executed for the first time out of factory, or in the on-die LAA register, so that LAA algorithm needs to be executed every time the system's power is applied. Detailed LAA method is described later.

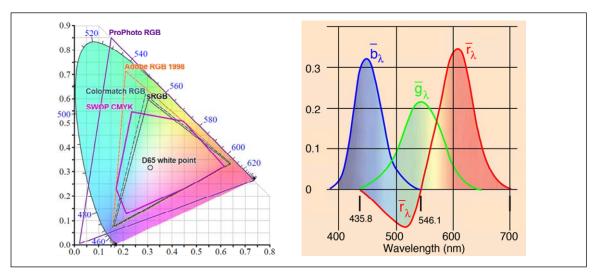

The MCU issues PWM data to the addressed slave device, e.g., IS32FL3202, to control each LED's color and brightness. The PWM data that is issued by the MCU is pre-processed, including various color space conversion and optionally gamma correction.

Each device is individually calibrated to compensate for LED production variations, and the calibrated parameters can be stored in an on-die, non-volatile, one-time-programmable memory, OTP. The parameters that are stored in this OTP is retrieved during system initialization and are copied to the corresponding accessible registers for operation.

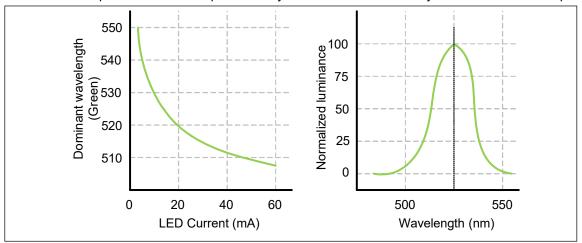

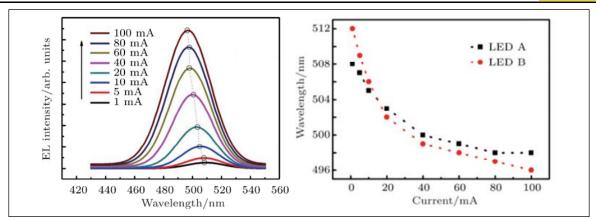

The LED driver controller inside IS32FL3202 measures temperature periodically and adjusts PWM duty cycle accordingly for each LED channel to maintain a constant luminance that is set at room temperature over wide temperature range (-40°C to 125°C). The device temperature is measured and obtained via an integrated analog-digital converter (ADC).

Besides the temperature measurement, the ADC can also measure various other analog parameters. These measurements are always triggered by a command from the host. The result of the corresponding ADC conversion can be read by a host command.

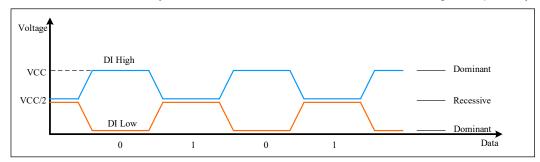

#### Simplified CAN PHY Format

A pair of LUMI PHY, one for receiving incoming signal and one for driving the next IS32FL3202 in the daisy chain. is integrated inside ISFL323202, using VCC as bias, which timing is shown in Figure 5. It can communicate with external, commercial CAN PHY directly if it is also biased with the same VCC for voltage compatibility.

Figure 5 IO Timing On Lumibus: Adopted From CAN Bus; Maximum Voltage Swing Is ±Vcc/2.

#### System Power up and Operation

All IS32FL3202 slaves are configured as downstream mode after power up, e.g., from host to the daisy chained devices, ready for write operation. The system becomes upstream from slave to host only during read respond operation. Read operation is mainly for error status polling, but all registers can be read for diagnosis and calibration purpose. All commands to slaves are initiated by the system host, which are described in detail later. The minimum and maximum bandwidth of Lumibus is 0.1Mbps and 2Mbps.

After VCC is applied, before any write operation, each IS32FL3202 device has an internal power up sequence to carry out a number of operations, e.g., read out 256-bit content from OTP non-volatile memory to its corresponding OTP content registers for operation. Consequently, a minimal of 100µs is required for the host to initiate the first host command.

The system operation can start after all configuration is finished. In most cases, the default values in the configuration registers, in conjunction with the OTP content registers, are sufficient for proper operation without any change. The host only need to send proper PWM values to the downstream devices.

Inside IS32FL3202, periodically the temperature sensor will automatically read the temperature sensor, which is used to compensate for the LED color change. Temperature compensation only takes place at the PWM boundaries.

It is recommended for the host to poll each device's error status register periodically.

The host communicates with slaves via UART communication protocol described below.

#### **Lumibus Format**

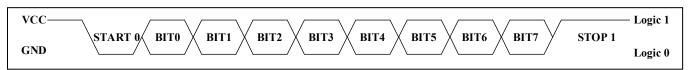

#### **UART Data Format**

Figure 6 UART Data Byte Format

Between data frames, at least one bit is required as STOP bit, it is recommended that the host use 2-bit stop bit.

Protocol: UART Protocol (not including special command)

| CMD Frame<br>Header | Device ID | Register Start<br>Address | N Bytes of Data | CRC checksum |

|---------------------|-----------|---------------------------|-----------------|--------------|

| 1 Byte              | 1 Byte    | 1 Byte                    | N Bytes         | 2 Bytes      |

Device ID is established via Location Address Assignment (LAA) method during the first system initialization process.

#### **Lumibus Communication Sequence**

#### **Bus Reset**

When the system is powered up, normally the system host is initialized before initializing peripherals. Before initializing Lumibus devices, a bus reset operation is required.

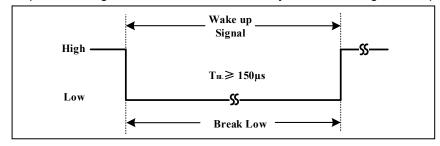

When more than 150µs are asserted (pulled low), the host is issuing a bus reset command for bus reset operation. Upon receiving the bus reset command, all devices on the Lumibus will be in reset status. This operation can be optionally performed by the host for a number of application scenarios: (1) during system power up, as stated above, (2) host watchdog time is expired, (3) Lumibus communication fault is detected, illustrated as in the following diagram:

#### Host watchdog time is expired or host detect communication fault

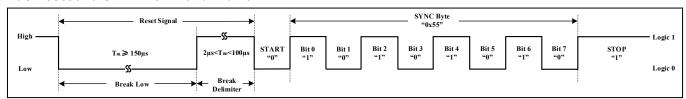

#### **Bus Reset and SYNC Command Frame**

Figure 7 Bus Reset and SYNC Command

Break Low time (T<sub>BL</sub>): min time 150µs

Break Delimiter time (TBD): Greater than 2µs, max timeout 100µs

SYNC 0x55: The first SYNC bit length is decided by lowest baud-rate (>=100Kbps)

Before communication, the host needs to first send a bus reset comment to reset all slaves' Lumibus status.

#### **Bus Reset IFG**

Figure 8 Bus Reset IFG (Single Device)

Figure 9 Bus Reset IFG (Cascade Application)

For host, it is necessary to waiting an IFG (Inter-Frame Gap) between sending the Bus Reset and next frame data. As shown in Figure 8 and Figure 9, the time of IFG need greater than 8bits baud rate, or greater than [8+ (N-1) ×11] bits baud rate in cascade application, where N is the number of devices in a chain.

One complete UART frame can be received successfully even if the frame is not sent continuously. CRC error could be determined by reading back the written data byte.

If host's watch dog time is disabled or time laps is within watchdog time

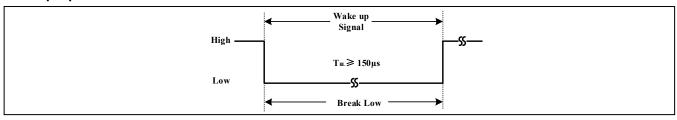

### **Wakeup Operation**

Figure 10 Wake up Signal

After IS32FL3202 enters power saving mode, it can be awakened by a break low signal ≥150µs.

**Writing Operation**

| Byte Types                  | Number of Bytes |

|-----------------------------|-----------------|

| CMD Frame Header Byte       | 1               |

| Device ID Byte              | 1               |

| Start Register Address Byte | 1               |

| Register Date Byte          | N (1~16)        |

| CRC Bytes                   | 2               |

| Total                       | N+5             |

Write Command Frame Structure (write: N = 1~16)

| CMD Frame<br>Header | Device ID | Register Start<br>Address | N Bytes of Data | CRC_L  | CRC_H  |

|---------------------|-----------|---------------------------|-----------------|--------|--------|

| 1 Byte              | 1 Byte    | 1 Byte                    | N Bytes         | 1 Byte | 1 Byte |

**Reading Operation**

| Byte Types                  | Number of Bytes |

|-----------------------------|-----------------|

| CMD Frame Header Byte       | 1               |

| Device ID Byte              | 1               |

| Start Register Address Byte | 1               |

| CRC Bytes                   | 2               |

| Total                       | 5               |

#### **Read Command Frame Structure**

| CMD Frame Header | Device ID | Register Start Address | CRC_L  | CRC_H  |

|------------------|-----------|------------------------|--------|--------|

| 1 Byte           | 1 Byte    | 1 Byte                 | 1 Byte | 1 Byte |

Response

| Byte Types            | Number of Bytes |

|-----------------------|-----------------|

| RSP Frame Header Byte | 1               |

| Device ID Byte        | 1               |

| Register Date Byte    | N (1~16)        |

| CRC Bytes             | 2               |

| Total                 | N+4             |

**Response Frame Structure**

| RSP Frame Header | Device ID | Register Data | CRC_L  | CRC_H  |

|------------------|-----------|---------------|--------|--------|

| 1 Byte           | 1 Byte    | N Bytes       | 1 Byte | 1 Byte |

#### **Burst Read Command Format Structure**

| CMD Frame Header | Device ID | Register Start Address | CRC_L       | CRC_H        |

|------------------|-----------|------------------------|-------------|--------------|

| 0b1110xxxx       | Address n | Start Register Address | CRC_L [7:0] | CRC_H [15:8] |

| 1 Byte           | 1 Byte    | 1 Byte                 | 1 Byte      | 1 Byte       |

CMD Frame Header: 0b1110xxxx(0xEx), determines read data length,

Bit [3:0] = [0000] = 1 byte, ..., Bit [3:0] = [1111] = 16 Bytes;

Device ID: Address n, n is the number of bursts read devices

CMD Frame Header lower 4 bits indicates the total number of bytes (1 - 16 bytes) and Reg Address indicates the starting address.

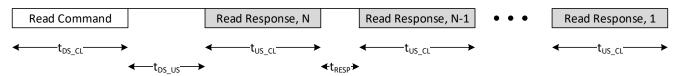

When the host issues the burst read command in broadcast mode, the host can read all register contents from device address #N (the last device) to #1 as shown in the following timing diagram. It starts from device #N, and with a time t<sub>DS\_US</sub> and t<sub>RESP</sub> between devices for the next device read data, until the first device data is read. Note that when using this feature, device address must be assigned consecutively.

Where the t<sub>DS\_US</sub>>17bits (follow communication baud rate) and t<sub>RESP</sub>>17bits (follow communication baud rate).

#### **Special Command**

| Byte Types            | Number of Bytes |

|-----------------------|-----------------|

| CMD Frame Header Byte | 1               |

| Device ID Byte        | 1               |

| CRC Bytes             | 2               |

| Total                 | 4               |

**Special Command Frame Structure**

| CMD Frame Header | Device ID | CRC_L  | CRC_H  |

|------------------|-----------|--------|--------|

| 1 Byte           | 1 Byte    | 1 Byte | 1 Byte |

Please check the below CMD and RSP Frame Header for more information about the special command CMD Frame Header.

#### **CMD and RSP Frame Header**

|                       | D7          | D6  | D5   | D4          | D3 | D2 | D1 | D0 |

|-----------------------|-------------|-----|------|-------------|----|----|----|----|

| CMD Frame Header      | FRM_TYPE =1 | W/R | BCON | DATA[4:0]   |    |    |    |    |

| Response Frame Header | FRM_TYPE=0  | -   | -    | - RESP[3:0] |    |    |    |    |

#### **CMD Frame Header**

D7(FRM\_TYPE): 0 = Response Frame;

1 = Command Frame;

D6(W/R): 0 = write;1 = read;

D5(BCON): 0 = normal single device writes and read command;

1 = broadcast write and read command; When BCON = 1 and Device ID = FFh,

broadcast to all devices;

D4~D0(DATA [4:0]): When DATA [4] =0: the DATA [3:0] determines transmit data length,

DATA [4:0] = [00000] = 1 byte, ..., DATA [4:0] = [01111] = 16 Bytes;

When DATA [4] =1: the DATA [3:0] represents special write command, as below:

DATA [4:0] = [11100] PWM SYNC synchronization, works with broadcast mode to reset all

slaves' PWM counters

DATA [4:0] = [11110] Registers reset command: to reset all function registers to default values (address  $0x00\sim0x1D$ ) when receiving this command (support both normal command and broadcast command);

iorniai command and broadcast command,

DATA [4:0] = [11000] PWM data update latch command; PWM data is loaded upon when receiving this command (support both normal command and broadcast command);

#### Response Frame Header

$D7(FRM\_TYPE)$ : 0 = Response Frame;

1 = Command Frame;

D6:D4 are reserved

D3~D0(RESP [3:0]): Response data length, RESP [3:0] = [0000] = 1 byte, ..., RESP [3:0] = [1111] = 16 bytes;

#### **Device ID Byte**

Device ID [7:0]: Device address is assigned by LAA method

#### **CRC Bytes**

The host sends command to IS32FL3202 using CRC-16-IBM standard for CRC checksum calculation, which will cover the whole frame data, e.g., CMD Frame Header, Device ID, Register Address, N Bytes of Data. Lower CRC byte first followed by higher CRC byte.

| CMD Frame Header | Device ID | Register Start<br>Address | N Bytes of Data | CRC_L  | CRC_H  |

|------------------|-----------|---------------------------|-----------------|--------|--------|

| 1 Byte           | 1 Byte    | 1 Byte                    | N Bytes         | 1 Byte | 1 Byte |

The following is a reference CRC checksum C code.

When IS32FL3202 sends back CRC to the host, the data needs to be bit reversed then compare with the CRC data. The following is a reference CRC reverse bit checksum code.

```

Uint8 reverse_byte(Uint8 byte)

// First, swap the nibbles

byte = (((byte \& 0xF0) >> 4) | ((byte \& 0x0F) << 4));

// Then, swap bit pairs

byte = (((byte \& 0xCC) >> 2) | ((byte \& 0x33) << 2));

// Finally, swap adjacent bits

byte = (((byte \& 0xAA) >> 1) | ((byte \& 0x55) << 1));

// We should now be reversed (bit 0 <--> bit 7, bit 1 <--> bit 6, etc.)

return byte;

The following is a reference code for checking the returned data against CRC data.

bool is_crc_valid(Uint8 *rx_buf, Uint8 crc_start)

Uint16 crc calc; // Calculated CRC

Uint8 crc_msb, crc_lsb; // Individual bytes of calculated CRC

// Calculate the CRC based on bytes received

crc calc = crc 16 ibm(rx buf, crc start);

crc lsb = (crc calc & 0x00FF);

crc msb = ((crc calc >> 8) \& 0x00FF);

// Perform the bit reversal within each byte

crc_msb = reverse_byte(crc_msb);

crc_lsb = reverse_byte(crc_lsb);

// Do they match?

if((*(rx buf + crc start) == crc lsb) && (*(rx buf + crc start + 1) == crc msb))

return TRUE;

Else

{

return FALSE;

}

}

```

#### LAA, Location Address Assignment

Location Address Assignment method (LAA) refers to the method that is used to automatically assign a unit address to the equally built slave devices, e.g., ISFL323202, that are located within a Lumibus system.LAA method is used in conjunction with Lumissil's proprietary bus, Lumibus as described earlier, that is a modification of CAN bus to take advantage of its well-established physical layer definition, as well as UART protocol, for its robust, chip-to-chip communication.

#### **LAA Basic Function**

Each IS32FL3202 device has a built-in LAA switch. The LAA line is routed through this built-in LAA switch of each Lumibus slave unit.

During normal operation, the LAA switch of the Lumibus slave unit is always closed. The only exception is during the LAA configuration process, when the LAA switch is opened to disconnect all following Lumibus slave units from the Lumibus bus communication.

The LAA configuration process starts with an LAA initialization command. This command causes all Lumibus slave units to reset the NAD (Network Address) and open their respective LAA switch. As a consequence, the first Lumibus slave unit (next to the Lumibus master) is the only Lumibus slave unit that can still receive LAA commands. Thus, the following NAD assignment command will be solely received by the first LAA slave unit. When the NAD command has been correct, the new NAD will be accepted and the LAA switch will be closed to enable the following Lumibus slave unit to receive LAA messages. Thus, with the next NAD assignment command the following unassigned Lumibus slave unit will be assigned with a new NAD and afterwards also closes its LAA switch. This procedure continues until all Lumibus slave units are assigned with its dedicated NAD. Afterwards all LAA switches are closed and a command is sent to inform all Lumibus slave units about the LAA process closure. In the following section "Configuration Flow" further details how the LAA configuration process are provided.

The following system block diagram shows the LAA configuration flow (write), as well as SNPD read back flow. Normal data follows the same data flow.

## **LAA Configuration Flow**

The LAA uses five LAA node configuration services. They are distinguished via SNPD sub functions. The LAA node configuration services are listed in Table 1.

#### **Table 1 LAA SNPD Sub Functions**

| Table 1 EAA ON D Gab 1 directions |                                                 |  |  |  |  |

|-----------------------------------|-------------------------------------------------|--|--|--|--|

| SNPD Sub Function                 | Service Description                             |  |  |  |  |

| LAA Initialization                | Starts LAA configuration process                |  |  |  |  |

| LAA NAD Assignment                | Assigns LAA slave with new NAD                  |  |  |  |  |

| LAA Finished                      | Informs about LAA configuration process closure |  |  |  |  |

| LAA read NAD register             | Read out NAD from OTP content NAD register      |  |  |  |  |

| LAA write NAD to OTP NVM          | Write new NAD to OTP NVM register               |  |  |  |  |

| LAA read from OTP NVM             | Read out NAD From OTP NVM register              |  |  |  |  |

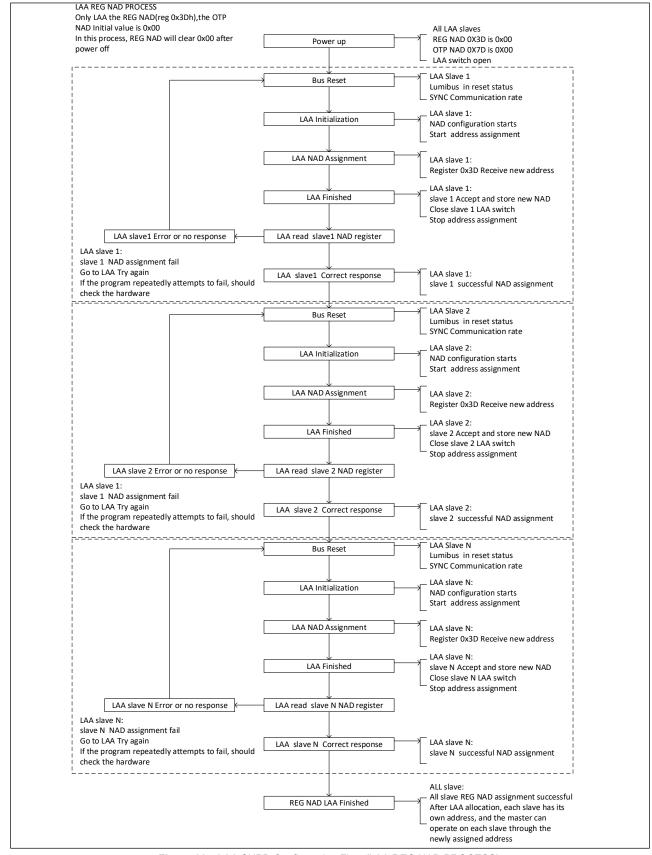

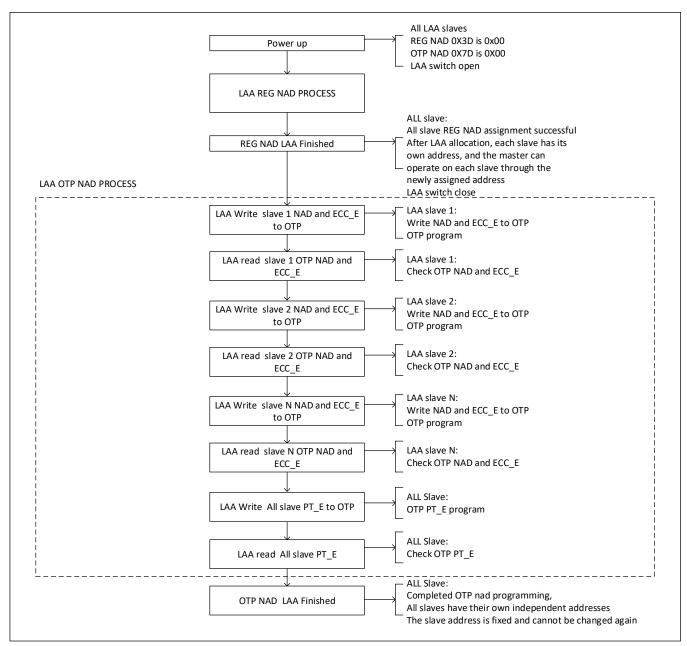

Figure 11a LAA SNPD Configuration Flow (LAA REG NAD PROCESS)

Figure 11b LAA SNPD configuration flow (LAA OTP NAD PROCESS)

Figure 11a and 11b illustrate the LAA configuration flow, which reflects a more detailed explanation in terms of the timing relationship of the flow. Its corresponding commands are shown in Table 1. The LAA process is framed with a starting and a ceasing service. The LAA SNPD sub function LAA Initialization starts the configuration and causes all LAA slave units to open their LAA switch. The LAA process closure is communicated with the LAA SNPD sub function LAA Finished.

With the LAA SNPD sub function LAA NAD Assignment an LAA slave unit is allocated with a dedicated NAD. The NAD will be accepted only, if the LAA slave unit has not been assigned with a new NAD, yet, and the LAA switch is still open. After NAD acceptance, the LAA switch is closed. LAA NAD Assignment is ignored from already assigned LAA slave units.

In order to check whether the new NAD has been accepted, the Lumibus master can optionally request acknowledgment from the last assigned LAA slave unit by means of a positive Lumibus slave response. This approach bases on a handshake principle.

LAA NAD Assignment is sent to each LAA slave unit, respectively, until all LAA slave units have been assigned with a new NAD according to the installation location. When all LAA slave units have accepted a new NAD, then all LAA switches are closed again.

During LAA configuration the SNPD sub function LAA NAD assignment shall be accepted from unassigned LAA slaves only, i.e., all LAA slaves with assigned new NAD will ignore this SNPD sub function. Thus the first Lumibus slave closed the LAA switch and shall ignore any further LAA NAD assignment and the second Lumibus slave can receive Lumibus frames from the Lumibus master and shall accept a valid LAA NAD assignment. After successful assignment of new NAD, the second Lumibus slave shall also close its LAA switch and consequently enable the next Lumibus slave in the daisy chain for LAA assignment.

With this configuration flow each LAA slave will be assigned one by one with a new NAD, typically starting from 1 and assigned in an ascending order. Note that the SNPD process for all LAA slaves (from reception of LAA Initialization until reception of LAA Finished) shall be completed within 4s, because when Lumibus inactivity is detected an LAA slave shall close the LAA switch and enter bus sleep mode.

In the above flow, the assigned address, NAD, to each slave will be permanently stored in OTP. This flow's advantage is that after out of factory, the NAD of each slave is assigned and fixed; the system does not need to assign NAD to each slave every time during power up. The disadvantage is that in case there is any one, or more, slave that is broken and is replaced, the NAD flow needs to be executed once again in the shop to re-assign this NAD.

Alternatively, this LAA flow can be execute every time when the system is powered up; NAD is not stored in OTP. The NAD of each slave each time is assigned automatically but it will take longer initialization time, especially if there are many slaves in the chain and in the system.

#### **LAA Initialization Command**

Host needs to first send this LAA Initialization command before any LAA NAD Assignment action. After IS32FL3202 receives this LAA Initialization command, register 0x3D then can use LAA NAD Assignment command for NAD assignment.

| CMD Frame Header | Device ID | Register Address | CNAD | LDAT | CRC_L | CRC_H |

|------------------|-----------|------------------|------|------|-------|-------|

| 0xA1             | 0xFF      | 0xAC             | 0x7F | 0x01 | 0xAC  | 0x1C  |

#### **LAA NAD Assignment Command**

LAA NAD assignment command is to change register 0x3D for new NAD address.

| CMD Frame<br>Header | Device ID | Register<br>Address | Register Data | CRC_L  | CRC_H  |

|---------------------|-----------|---------------------|---------------|--------|--------|

| 0x80                | iNAD      | 0x3D                | NAD           | 1 Byte | 1 Byte |

Where iNAD is current NAD stored in 0x3D (Initial value = 0x00), NAD is the target new address.

#### **LAA NAD Finished Command**

After completing LAA NAD Assignment Command to change IS32FL3202 NAD address, host needs to send this LAA NAD Finished Command to complete NAD assignment action. After receiving LAA NAD Finished Command, LAA NAD Assignment will become inactive, and will become active again only upon receiving another LAA Initialization Command.

| CMD Frame Header | Device ID | Register Address | CNAD | LDAT | CRC_L | CRC_H |

|------------------|-----------|------------------|------|------|-------|-------|

| 0xA1             | 0xFF      | 0xAC             | 0x7F | 0x03 | 0x2D  | 0xDD  |

### LAA read NAD register

#### Read 0x3D register to obtain current NAD:

| CMD Frame Header | Device ID | Register Address | CRC_L  | CRC_H  |

|------------------|-----------|------------------|--------|--------|

| 0xC0             | iNAD      | 0x3D             | 1 Byte | 1 Byte |

Where iNAD is current NAD stored in 0x3D (Initial value = 0x00), and iNAD becomes the target new address after LAA.

#### Response:

| RSP Frame Header | Device ID | Register Data | CRC_L  | CRC_H  |

|------------------|-----------|---------------|--------|--------|

| 0x00             | iNAD      | 1Byte         | 1 Byte | 1 Byte |

RSP Frame Header: 0x00 is read data length

Device ID: iNAD is current NAD stored in 0x3D (Initial value = 0x00), and iNAD becomes the target new address

after LAA

Register Data: the data of 0x3D register

#### LAA: Write NAD to OTP

| CMD Frame<br>Header | Device ID | Register<br>Address | Data of 0x7D<br>Register | Data of 0x7E<br>Register | CRC_L  | CRC_H  |

|---------------------|-----------|---------------------|--------------------------|--------------------------|--------|--------|

| 0x81                | iNAD      | 0x7D                | NAD                      | ECC_E                    | 1 Byte | 1 Byte |

No write operation if (iNAD=0 or iNAD !=NAD or ECC\_error)

| CMD Frame<br>Header | Device<br>ID | Register<br>Address | Data of 0x7D<br>Register | Data of 0x7E<br>Register | Data of 0x7F<br>Register | CRC_L  | CRC_H  |

|---------------------|--------------|---------------------|--------------------------|--------------------------|--------------------------|--------|--------|

| 0x82                | iNAD         | 0x7D                | NAD                      | ECC_E                    | PT_E                     | 1 Byte | 1 Byte |

The difference between 0x81 and 0x82 is that in 0x82, protect bit status is written into OTP while in 0x81, this bit is not written into OTP.

If iNAD = 0, or iNAD is not the current value, or when there is ECC error, the data will not be written into OTP.

#### LAA: Read NAD and ECC from OTP

| CMD Frame Header | Device ID | Register Address | CRC_L  | CRC_H  |

|------------------|-----------|------------------|--------|--------|

| 0xC1             | iNAD      | 0x7D             | 1 Byte | 1 Byte |

Response NAD and ECC from OTP

| RSP Frame Header | Device<br>ID | NAD Register(0x7D)<br>Data | ECC Register(0x7E) Data | CRC_L  | CRC_H  |

|------------------|--------------|----------------------------|-------------------------|--------|--------|

| 0x01             | iNAD         | 1Byte                      | 1Byte                   | 1 Byte | 1 Byte |

RSP Frame Header: 0x01 is read data length

Device ID: iNAD is current NAD stored in 0x7D (Initial value = 0x00), and iNAD becomes the target new address after LAA

Register Data: the data of 0x7D and 0x7E register

#### LAA: Read NAD, ECC and PT C from OTP

| CMD Frame Header | Device ID | Register Address | CRC_L  | CRC_H  |